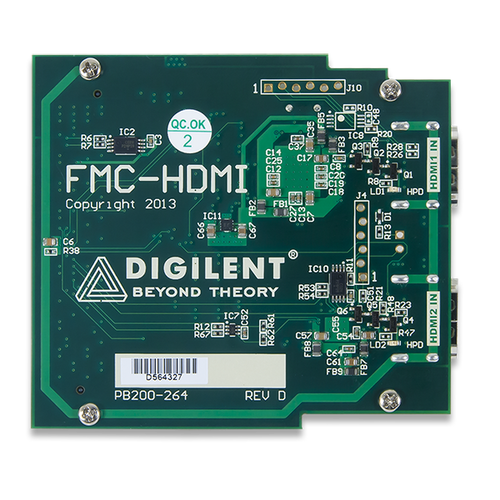

Product Description

The FMC-HDMI extends FMC-compatible FPGA systems with two HDMI Type A input ports. It’s extremely useful for image or video processing applications. One of the ports features a fully-fledged HDMI 1.4 receiver with CEC, HDCP, audio, and 3D TV support. The other port provides cable equalization and buffering for HDMI signals, leaving the decoding up to the user.

Which port is more appropriate to use depends on the application. The receiver port is user-friendly, hiding the complexities of the HDMI protocol. Its simple pixel bus interface spans a wide range of voltages and is easy to design in any FPGA environment. The receiver also hides the implementation details of auxiliary features, like CEC or audio embedded in the video stream. The second port provides signal conditioning only, so the HDMI protocol needs to be implemented in the FPGA. This offers video processing flexibility at the price of complexity. Also, the TMDS I/O standard defined by the HDMI protocol requires a 3.3V VADJ, which might limit the compatibility with certain carrier cards. The EEPROM pre-programmed with a ready-to-use EDID should prove to be a good starting point. Both ports are backwards-compatible with DVI.

Stats:

Connector(s):

- FMC LPC Mezzanine

- 2 x HDMI type A

Features:

- Analog Devices ADV7611 Low Power 165 MHz HDMI Receiver

- Analog Devices AD8195 1:1 HDMI/DVI Buffer with Equalization

- Adds two HDMI input ports to a compatible FMC carrier card

- HDMI receiver & buffer

- On-board EDID EEPROM

- Supports Full HD 1080p @ 60 MHz

- Auxiliary features such as CEC, Audio

- HDMI Port 1 includes a decoder which hides unneccessary complexity from the user

- HDMI Port 2 provides signal conditioning and buffering only, leaving the decoding up to the user

- Wide range of VADJ (1.8V-3.3V) supported for HDMI Port 1

- On-board pre-programmed EDID EEPROM for HDMI Port 2